RISC structure and its advantages and disadvantages

Source: InternetPublisher:消失的歌 Keywords: cpu RISC Updated: 2025/02/18

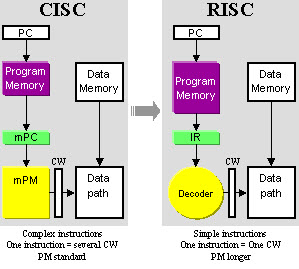

The central processing unit architecture has the capability from the "instruction set architecture" to its design work. The architectural designs of CPU are RISC (Reduced Instruction Set Computing) and CISC (Complex Instruction Set Computing). CISC is able to perform addressing modes or multi-step operations in one instruction set. This is the design of the CPU where one instruction performs many low-level operations. For example, memory storage, arithmetic operations, and loading from memory.

RISC is a CPU design strategy based on the interpretation that a simplified instruction set provides higher performance when combined with a microprocessor architecture that is able to execute instructions using a few microprocessor cycles per instruction.

In this article, microcontroller development engineers mainly introduced the RISC structure, its advantages and disadvantages.

1. What is RISC architecture?

RISC (Reduced Instruction Set Computer) is used in portable devices due to its high energy efficiency. For example, Apple iPod and Nintendo

DS. RISC is a microprocessor architecture that uses a highly optimized instruction set. RISC, on the contrary, reduces the cycles per instruction at the expense of the number of instructions per program. Pipelining is one of the unique features of RISC. It performs by overlapping the execution of multiple instructions in a pipelined manner. It has a high-performance advantage over CISC.

RISC processors use simple instructions and execute them in one clock cycle.

2. Characteristics of RISC architecture

1.Simple instructions are used in RISC architecture.

2.RISC helps and supports some simple data types and synthesizes complex data types.

3.RISC uses simple addressing modes and fixed-length instructions for pipeline processing.

4.RISC allows any register to be used in any context.

5. Single cycle execution time.

6. By separating the "LOAD" and "STORE" instructions, you can reduce the amount of work the computer can perform.

7.RISC contains a large number of registers to prevent various interactions with memory.

8. In RISC, pipelining is easy because the execution of all instructions will be completed in a uniform time interval (i.e., one click).

9. In RISC, more RAM is required to store assembly level instructions.

10. Reduced instructions reduce the number of transistors in RISC.

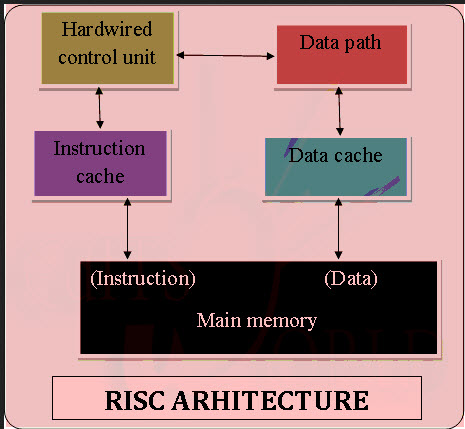

11.RISC uses Harvard memory model which means it is Harvard architecture.

12. Compilers are used to perform conversion operations, converting high-level language statements into their form of code.

3. Advantages of RISC architecture

1.RISC (Reduced Instruction Set Computing) architecture has a set of instructions so that high-level language compilers can generate more efficient code.

2. Due to its simplicity, it allows free use of space on the microprocessor.

3. Many RISC processors use registers to pass parameters and save local variables.

4.RISC functions use only a few parameters, and RISC processors cannot use call instructions, so fixed-length instructions that are easy to pipeline are used.

5. Operation speed can be maximized and execution time can be minimized.

6. The number of instruction formats required is very small, and the number of instructions and addressing modes required are also very small.

4. Disadvantages of RISC Architecture

1. Generally, the performance of a RISC processor depends on the programmer or compiler because the knowledge of the compiler plays a vital role in changing CISC code into RISC code.

2. When rearranging CISC code into RISC code (called code expansion), there will be an increase in size. And, the quality of this code expansion will again depend on the compiler as well as the instruction set of the machine.

3.The L1 cache of RISC processors is also a disadvantage of RISC, where these processors have a large memory cache on the chip itself. In order to provide instructions, they require a very fast memory system.

- What is a FinFET? What are the advantages and disadvantages of FinFET?

- How are diodes made using semiconductors?

- Symbol/working principle/type/characteristics/application scenarios of depletion-mode MOSFET

- What factors are related to the hysteresis loss of the transformer? Can the hysteresis loss be reduced?

- What is power factor and three ways to improve it

- DIY a decorative lamp

- How to Build a Simple Temperature Indicator Circuit Using NTC and PTC Thermistors

- Important things to know about PCB routing and how to design the right routing for your PCB

- Ceramic filter structure/working principle/characteristics/application

- Tutorial on building a NOT gate using BJT transistors

- CPU and house majong circuit using AK3200M chip

- Microprocessor reset circuit b

- CPU power supply circuit using RT9214 chip

- Internal structure of RT9245 chip

- 3-phase CPU power circuit using HIP6301 and HIP6601 chips

- 2-phase CPU power supply circuit using HIP6302 and HIP6602 chips

- UM5020C voice processing chip CPU working mode drives the speaker

- Interface circuit between DAC0808 and CPU

- Multi-channel AD converter ADC0809 connected to Z80CPU

- Typical circuit connecting MAX1204 to CPU

京公网安备 11010802033920号

京公网安备 11010802033920号