A Tool for Exploring Digital InterfacesGlasgow is intended for hardware designers, reverse engineers, digital archivists, electronics hobbyists, and anyone else who wants to communicate with a wide selection of digital devices with minimum hassle. It can be attached to most devices without additional active or passive components, and it provides extensive protection from unexpected conditions and operator error.

The Glasgow hardware can support many digital interfaces because it uses reconfigurable logic. Instead of offering just a small selection of standard hardware supported interfaces, it uses an FPGA to adapt — on the fly — to the task at hand without compromising performance or reliability, even for unusual, custom or obsolete interfaces.

The Glasgow software is a set of building blocks designed to eliminate system complexity. Each protocol is packaged into a self-contained applet that can be used directly from the command line or integrated into a more complex system. Using Glasgow does not require any programming knowledge, though it is much more powerful if you know a bit of Python.

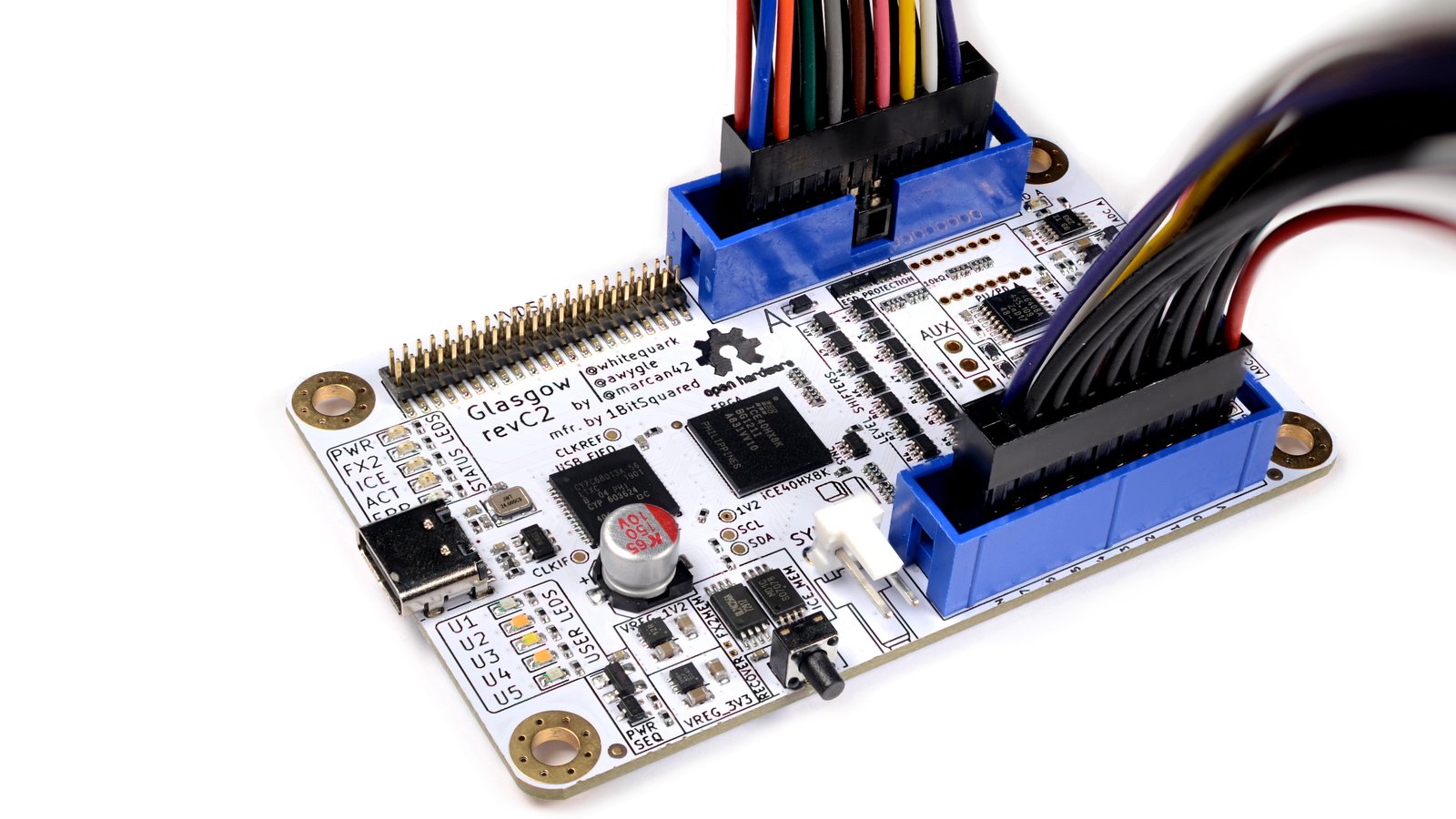

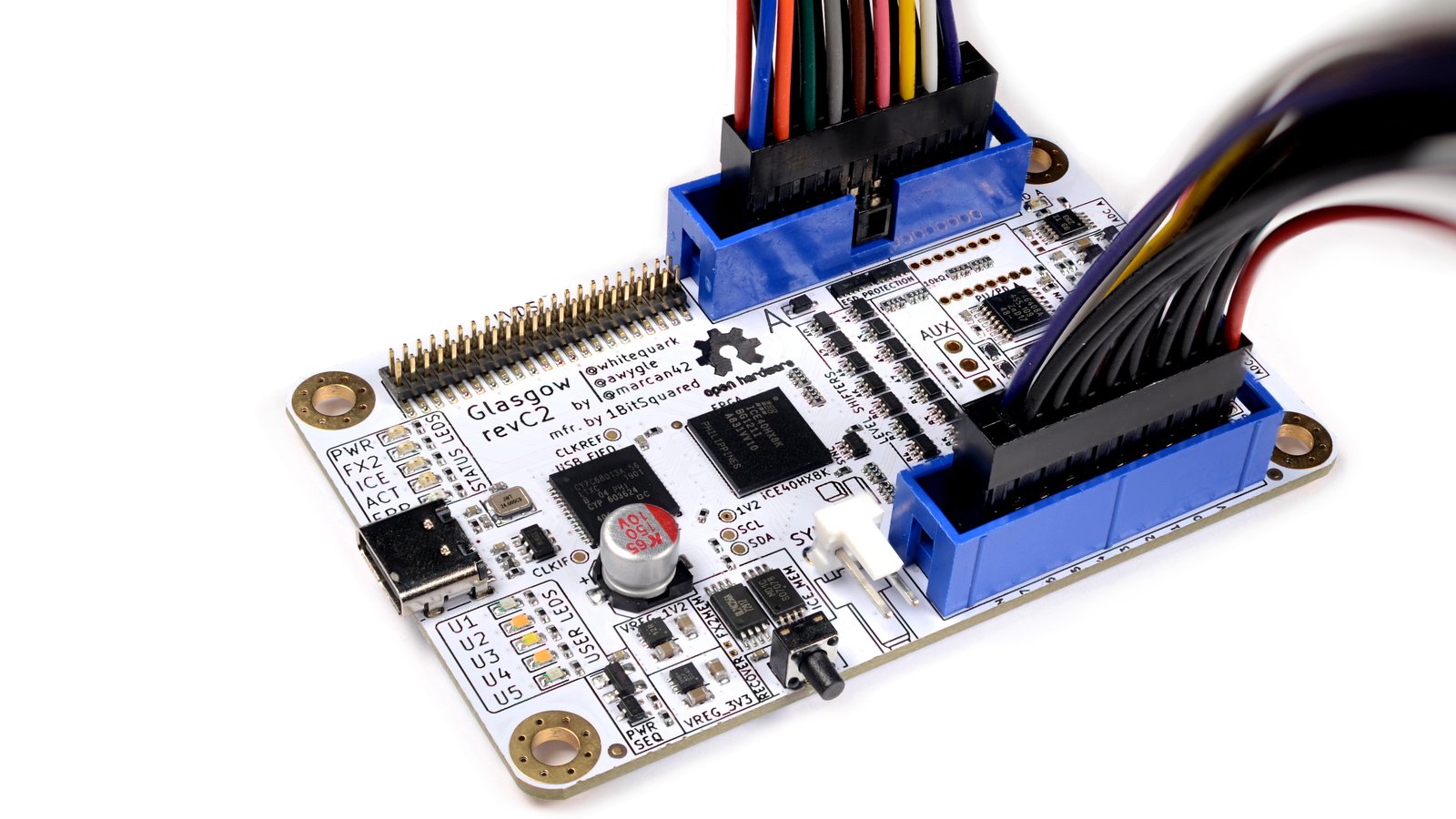

Glasgow revC2

Use CasesTo illustrate some strengths of Glasgow, here are a few usage examples.

USB-to-Serial adapterGlasgow can be used as a USB-to-serial adapter, but better.

Unlike traditional serial adapters it can auto-detect the target voltage and "mirror" it. It will auto-detect the baud rate of the target and follow it on the fly. It can directly interface to inverted signal UART interfaces, which would ordinarily require additional debugging components, like buffer transistors.

Environmental Sensor LoggerGlasgow has built-in support for InfluxDB. So any applet that reads out sensors can directly log the data and you can visualize them in Grafana with very minimal effort. We already have support for some CO2 and particle sensors.

Glasgow-InfluxDB-Grafana Temperature, Humidity, CO2 log from an SCD30 sensor. Click to enlarge.

RGB LED InterfaceToday there are a lot of different LED display technologies available. Like "intelligent" RGB LEDs with built in PWM controllers, for example WS2812 or APA102. There are LED matrix display panels with myriad of shift register based interfaces like HUB75, HUB75e, HUB8, HUB12 and many more.

All of them use fairly nonstandard protocols. From timing-driven one-wire interfaces, through fairly normal SPI interfaces to multichannel parallel shift register interfaces. Typical protocol adapters only provide a specific subset of hardware supported interfaces. Everything beyond that has to be implemented with so called bit-banging. Bit-banging means that the processor or the PC has to control I/O step from software, in some cases even through USB. This is cumbersome if not impossible due to the timing constraint and USB speed.

In the case of Glasgow, that can be easily reconfigured. It is possible to experiment and prototype with these devices quickly and with minimal hassle. Just a few lines of Amaranth HDL and Python and you are ready to go.

If you are interested how it is done, watch Attie implement HUB75 interface support.

SafetySafety is an important design requirement for Glasgow, we addressed it in multiple ways.

Protective caseWe designed a beautiful CNC-milled aluminum case to keep your Glasgow safe from damage — from short circuits on the bench or the exercise shorts in your travel bag. It’s available as an option.

Glasgow revC aluminum case. (Design and 3D rendering by @timonsku)

ESD, Under- and Over-Voltage protectionWorking with untested or unknown devices can be risky. Short circuits, electrostatic discharge, high voltages can quickly destroy our project or test equipment. Glasgow is ready for this. All I/O are ESD, over- and under-voltage protected. We have made sure that the hardware will survive a I/O and supply short and not reset, but rather detect a set current threshold fault and act accordingly thanks to I/O supply current monitoring.

E-Stop/ResetFor the urgent situations where one might want to quickly put Glasgow back in safe mode; we have added an easy to reach E-Stop/Reset button. It is located on the side of the board, so a quick squeeze of the Glasgow will bring it back into an electrically safe state. This button is hardwired to the Glasgow circuitry and results in a safe reset even if the software or gateware is faulty.

Glasgow revC aluminum case, E-Stop/Reset button and sync connector detail.

(Design and 3D rendering by @timonsku)

FeaturesGlasgow is already capable of performing these tasks:

Standard ProtocolsCommunicating via UARTAutomatically determining and following the baud rate of the

device under test

Initiating transactions via SPI or I²C

Receive I²C transactions

Logic analyzer, generates VCD file for analysis with GTKWave or Sigrok

Memory ChipsReading and writing 24-series EEPROMs

Reading and writing 25-series Flash memoriesDetermining memory parameters via SFDP

Reading and writing ONFI-compatible Flash memoriesDetermining memory parameters via ONFI parameter page

Reading and writing 27/28/29-series EPROMs, EEPROMs and Flash

memoriesDetermining the extent of floating gate charge decay and data

rescue

Microcontroller/CPU Programming and Debugging InterfacesProgramming and verifying AVR microcontrollers with SPI interface

Automatically determining unknown JTAG pinouts

Present JTAG interface to OpenOCD

Playing back JTAG SVF files

Debugging ARC processors via JTAG

Debugging some MIPS processors via EJTAG

Debugging some microcontrollers via SWD (WIP)

Probe microcontrollers via the TI Spy-Bi-Wire interface

Programming Microchip (Atmel) AVR microcontrollers via SPI

Programming Renesas M16C microcontrollers via UART

Programming Microchip MEC16xx embedded controllers via JTAG

Programming nRF24LE1 and nRF24LU1(+) microcontrollers

FPGA/CPLD Bitstream Programming InterfacesProgramming and verifying XC9500XL CPLDs via JTAG

Programming iCE40 FPGA FLASH and SRAM

Programming Xilinx Spartan-6 FPGAs via JTAG

Programming Xilinx XC500XL CPLDs via JTAG

Radio InterfacesCommunicating using nRF24L01(+) radios

Sensor InterfacesMeasuring temperature, pressure, and humidity with Bosh BMx280

sensors

Measuring voltage with AVIA Semiconductor HX711

Measuring voltage, current and power with TI INA260 sensors

Measuring air quality with Plantower PMx003 sensors

Measuring CO2, humidity, and temperature with Sensirion SCD30 sensors

Display & Video InterfacesDisplaying characters on HD44780-compatible LCDs

Displaying images on Pervasive Display EPD panels

Capturing video stream from RGB555 LCD bus

Displaying video via VGA

Displaying video via WS2812 LEDs

Audio InterfacesPlaying sound using sigma-delta digital to analog conversion

Synthesizing sound using a Yamaha OPL chip and playing it in real

time on a webpage

Other Misc InterfacesConfiguring TPS6598x USB PD controllers

Reading raw modulated data from 5.25" and 3.5" floppy drives

Communicate with IBM PS/2 peripherals

Receiving axis and button information from PS/2 mice

CAN Bus (WIP)

Note: features marked with "WIP" are Work In Progress, which means they are preview only and require more work or even a rewrite.

Most of the above can be done with only a Glasgow revC board, some wires, and — depending on the device under test – external power. In most cases no additional front end circuitry is needed.

Technical SpecificationsiCE40HX8K Lattice Semiconductor FPGA (supported by a fully open source FPGA

flow: Yosys, nextpnr, icestorm)

FX2 high-speed USB interface capable of 480 Mbps throughput

Two 8-channel I/O banks provide 16 highly flexible I/O

Each I/O bank has a dedicated programmable linear voltage regulator,

configurable from 1.8 V to 5 V and capable of providing up to 150 mA of power

Each I/O bank has a dedicated sense ADC capable of monitoring the I/O bank

voltage and current, with settable interrupt trigger thresholds

Each I/O is capable of a theoretical speed up to 100 MHz (actual speed

depends on many factors)

Each I/O has a dedicated voltage level shifter with individual direction

control

Each I/O has a dedicated, software controlled 10K Ohm pull-up/-down resistor

All I/O have ESD protection diodes

An optional set of 14 differential pair I/O, connected directly to the FPGA

without any front end circuitry, can be used for high speed interfaces (only

exposed on the circuit board, not accessible in combination with a case)

A dedicated SYNC connector

Five user-controllable LEDs connected to the FPGA

Five status LEDs

Legend

Click to enlarge.

Block Diagram

Comparison Table

Glasgow HardSploit Tigard JTAGulator HydraBus GoodFET GreatFET BusBlaster BusPirate UART Y Y Y Y Y N Y N Y SPI Y Y Y N Y Y Y N Y Parallel Y Y N N N N Y N N I2C Y Y Y N Y Y Y N Y JTAG/SWD Y Y Y Y Y Y Y Y Y Logic Analyzer Y Y Through Bitmagic Y Y Y Y N Y Extensibility FPGA FPGA FTDI MCU MCU MCU MCU CPLD MCU Interface CLI,API CLI,GUI,API CLI,GUI,API CLI CLI CLI CLI CLI CLI I/O count ¹ 16 64 14 24 44 9 100 9 7 Cascading ³ Y N N N N N N N N Indep. I/O ⁴ 2 banks 8 banks 1 bank 1 bank 1 bank 1 bank 1 bank1 bank1 bank I/O Voltages 1.8-5 V 3.3 V, 5 V 1.8 V, 3.3 V, 5.5 V 1.4-3.3 V 3.3 V 3.3 V 3.3 V 1.5-3.3 V 3.3 V, 5 V I/O Speed ¹ ² 100 MHz 25 MHz 25 MHz 15 kHz 42 MHz 1 Mbps 50 MHz 6 MHz 1 Mbps USB Type C Type Mini-B Type C Type Mini-B Type Micro-B Type Mini-B Type Micro-B Type Mini-B Type Mini-B Open Hardware Y N Y Y Y Y Y Y Y Cost $130 $320 ⁵ $39 $170 $80 $50 $100 $45 $37 ¹ In perfect conditions

² In Hz for target I/F bottleneck and bps for host I/F side bottleneck

³ Able to connect multiple devices together and synchronize them

⁴ I/O banks with independently controllable voltage

⁵ Unavailable at time of comparison

Built on Python & the Open Source iCE40 ToolchainGlasgow Interface Explorer is written in Python 3. The interface logic that runs on the FPGA is described using Amaranth, which is a Python-based domain-specific language (DSL). The supporting code that runs on the host PC is written in Python with asyncio. This way, the logic on the FPGA can be assembled on demand for any requested configuration, keeping it as fast and compact as possible, and code can be shared between gateware and software, removing the need to add error-prone "glue" boilerplate.

Glasgow would not be possible without the IceStorm, open source iCE40 FPGA toolchain, which is reliable and extremely fast.

For instance, it only takes a few seconds to rebuild the FPGA bitstream for the UART protocol. When developing a new applet, it is rarely necessary to wait for the toolchain.

Implementing reliable, high-performance USB communication is not trivial – packetization, buffering, and USB quirks add up. Glasgow abstracts away USB. On the FPGA, applet gateware writes to or reads from a FIFO. On the host, applet software writes to or reads from a socket-like interface. On a modern PC, idiomatic Python code can communicate at maximum USB 2 "high-speed" bandwidth. Moreover, this design is relatively future proof, as it can support different transports, such as Ethernet, without requiring changes to applet code.

Debugging new applets can be hard, especially where bi-directional buses are involved. Glasgow provides a built-in, cycle-accurate logic analyzer that can relate the I/O pin level and direction changes to commands and responses received and sent by the applet. The logic analyzer compresses waveforms and can pause the applet if its buffer is about to overflow.

Support & DocumentationGlasgow has been developed and refined over the last few years by a dedicated group of engineers. Many people have built their own hardware and are already using it in production. A lot of these early adopters are contributing additional applets and documentation. We welcome you to drop in to the Glasgow Discord channel or Glasgow Freenode IRC channel to talk about your ideas and ask questions!

For more technical discussion of Glasgow, please visit our GitHub Glasgow Organization.

We have a section of the 1BitSquared Forum dedicated to Glasgow.

Give esden and whitequark a follow on Twitter. Both of them regularly post Glasgow updates.

What Are You Getting?You get the following:

Glasgow revC hardware

Two fly-wire cables to easily connect the Glasgow to 0.1 inch pin headers or

IC hooks

Sync cable to connect multiple Glasgows together and synchronize them

USB-A to USB-C cable that supports the USB 2.0 HighSpeed standard

Glasgow revC2 with cables

The aluminum case option adds:

Anodized aluminum CNC milled case

Lightpipes for the LEDs

Screws

Glasgow revC aluminum case parts (Design and 3D rendering by @timonsku)

The case comes as a kit, and is easy to assemble. The case covers up some of the optional connectors on the Glasgow PCB. If you need access to these connectors, the bottom half of the case can be used alone, and will still provide protection to the underside of your Glasgow.

Glasgow revC CNC milled painted acrylic prototype (Design and prototype by@timonsku)

Timon designed the aluminum case and coordinates its production. He has many years of experience designing and producing cases for electronic products.

Snapshots from Glasgow revC2 prototype build process at 1BitSquared