Many systems require multiple low-jitter system clocks for mixed-signal processing and timing. The circuit shown in Figure 1 interfaces the ADF4351 integrated phase-locked loop (PLL) and voltage-controlled oscillator (VCO) to the ADCLK948 , which provides up to eight differential, low-voltage positive emitter-coupled logic (LVPECL) channels through one differential output of the ADF4351. ) output.

Modern digital systems often require the use of high-quality clocks with many logic levels that differ from the clock source. To ensure accurate power distribution to other circuit elements without loss of integrity, additional buffering may be required. Here, the ADF4351 integrated phase-locked loop (PLL) and voltage-controlled oscillator (VCO) interfaces with the ADCLK948, which can provide up to eight differential, low-voltage positive emitter coupled logic (LVPECL) outputs through one differential output.

Modern digital systems often require the use of high-quality clocks with many logic levels that differ from the clock source. To ensure accurate power distribution to other circuit elements without loss of integrity, additional buffering may be required. The interface between the ADF4351 clock source and the ADCLK948 clock fanout buffer is described here, and measurements show that the additive jitter associated with the clock fanout buffer is 75 fs rms.

The ADF4351 is a wideband PLL and VCO consisting of three independent multi-band VCOs. Each VCO covers a range of approximately 700 MHz (with some overlap between VCO frequencies). This provides a basic VCO frequency range of 2.2 GHz to 4.4 GHz. Frequencies below 2.2 GHz can be generated using the ADF4351's internal frequency divider.

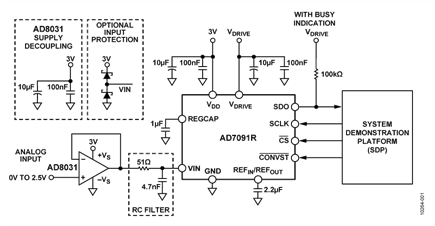

To complete clock generation, the ADF4351 PLL and VCO must be enabled, and the desired output frequency must be set. The output frequency of the ADF4351 is provided through the open-collector output at the RFOUT pin, which requires a parallel inductor (or resistor) and a DC blocking capacitor.

The ADCLK948 is a SiGe low-jitter clock fanout buffer that is ideal for use with the ADF4351 because its maximum input frequency (4.5 GHz) is just above the ADF4351 (4.4 GHz). Broadband rms additive jitter is 75 fs.

To simulate LVPECL logic levels, a 1.65 V DC common-mode bias level needs to be added to the CLK input of the ADCLK948. This can be achieved by using a resistor bias network. The lack of DC bias circuitry results in reduced signal integrity at the ADCLK948 output.

Blockdiagram

All reference designs on this site are sourced from major semiconductor manufacturers or collected online for learning and research. The copyright belongs to the semiconductor manufacturer or the original author. If you believe that the reference design of this site infringes upon your relevant rights and interests, please send us a rights notice. As a neutral platform service provider, we will take measures to delete the relevant content in accordance with relevant laws after receiving the relevant notice from the rights holder. Please send relevant notifications to email: bbs_service@eeworld.com.cn.

It is your responsibility to test the circuit yourself and determine its suitability for you. EEWorld will not be liable for direct, indirect, special, incidental, consequential or punitive damages arising from any cause or anything connected to any reference design used.

Supported by EEWorld Datasheet