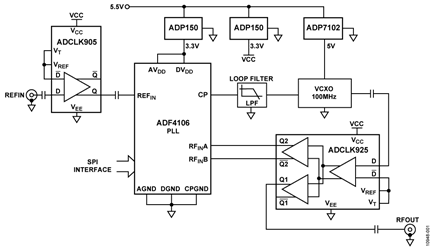

The circuit shown in Figure 1 is a high-performance phase-locked loop (PLL) that utilizes a high-speed clock buffer and a low-noise LDO to maintain low phase noise, even at low reference and RF frequencies.

For example, several ADI PLLs (such as the ADF4106 ) are rated for minimum reference frequency and RF input frequency of 20 MHz and 500 MHz respectively. Using the additional clock buffer shown in Figure 1, the frequency range can be reduced to a reference frequency of 10 MHz and an RF input frequency of 100 MHz.

The ADF4106 frequency synthesizer can be used to implement local oscillator functionality in the upconversion and downconversion portions of RF receivers, transmitters, signal analyzers, data generators, or any RF application that requires local oscillator functionality. When the frequency synthesizer is used with an external loop filter and voltage-controlled oscillator (VCO), a complete phase-locked loop (PLL) can be implemented.

The ADF4106 is an integer-N PLL where the channel step size is an integer N. The device has an RF frequency output range up to 6 GHz, is easy to use, and has a low phase noise rating, typically −223 dBc/Hz (normalized phase noise floor). Figure 1 shows the functional block diagram of a complete phase-locked loop using the ADF4106 in a low-noise single-frequency clock application, and Figure 2 shows its simplified schematic.

The low-noise 10 MHz reference source is buffered by the ADCLK905 and ac-coupled to REFIN of the ADF4106 PLL. The VCO is a low-noise, 100 MHz sine wave VCXO whose output is ac-coupled into the 50 Ω input load of the ADCLK925 . Interfacing this VCXO to the ADCLK925 is very simple since both devices are matched in terms of loading and signal level requirements. The ADCLK925 1:2 buffer output stage provides both the RFOUT signal and the required RF feedback signal to the PLL.

The ADF4106 PLL is powered by a dedicated 3.3 V ADP150 low-noise LDO, and the two clock buffers (ADCLK905, ADCLK925) are powered by a second ADP150. The ADP150's output voltage noise is only 9 μV rms, ensuring low phase noise for both the PLL and clock buffer.

The low-noise VCXO is powered by an ADP7102 low-noise 5 V linear regulator to reduce the effects of VCO pushing (equivalent to supply rejection).

Reference input clock buffer

The clock buffers for the REF IN and RF IN input stages of the PLL need to have low additive jitter, sufficient slew rate at the operating frequency, and sufficient signal swing to meet the requirements of the ADF4106.

The ADCLK905/ADCLK925 are ultrafast ECL clock/data buffers designed to minimize additive random jitter over a wide input slew rate range. They feature full-swing ECL emitter-coupled logic output drivers with 95 ps propagation delay and 60 fs random jitter. These devices have a rise/fall time (20% to 80%) of 60 ps (typ), which equates to a slew rate of approximately 8000 V/μs.

ADCLK905 is used to buffer the 10 MHz REFIN frequency source. Many applications typically use a reference frequency of 10 MHz. Depending on the available signal swing, the slew rate may not meet the ADF4106's 50 V/μsec (minimum) slew rate requirement. For example, a 10 MHz 0 dBm sine wave has a slew rate of only 20 V/μs.

The ADCLK905 was selected as the REF IN clock buffer to increase the slew rate of the 10 MHz frequency source. The low additive jitter of the ADCLK905 ensures that any additive jitter introduced by the REFIN clock buffer is minimal. The reference noise is not attenuated within the PLL bandwidth, thus keeping the reference noise low, which is a major factor when selecting components. The ADCLK905 has a low additive jitter of 60 fs, making it a sure choice. In a 50 Ω environment, input and output matching has a significant impact on performance. The input buffer of the ADCLK905 provides internal 50 Ω termination resistors for both D inputs simultaneously. The center tap VT between these two 50 Ω resistors is connected externally to the complementary D input and VREF pins . These pins are decoupled with a ceramic capacitor.

The PECL output stage of the ADCLK905 drives 800 mV from each terminal directly into a 50 Ω load terminated at V CC − 2 V. Termination is accomplished with a resistor termination on each ADCLK905 output. For V CC =3.3 V, a 150 Ω ground resistor is recommended.

The outputs are designed to drive transmission lines and the load impedance of each output pin should be matched. The ADCLK905 Q output is ac coupled into a 50 Ω load before being ac coupled to the high impedance input of the ADF4106 REF IN . Unused complementary Q outputs should be terminated with similar loads.

R input clock buffer

The ADCLK925 is used to buffer the 100 MHz RF IN from the low noise VCXO . RF IN requires a minimum slew rate of 320 V/μsec. ADCLK925 provides the required slew rate at the RF IN input. The ADCLK925's low additive jitter has little impact on PLL phase noise performance. The ADCLK925's 1:2 output stage simplifies feedback to the PLL, eliminating the need for dividers and matching components.

The PECL output stage drives 800 mV from each terminal directly into a 50 Ω load terminated at V CC − 2V. This is accomplished without the use of an additional power supply via a 150 Ω resistor to ground, as shown in Figure 2. The RF IN input stage of the ADF4106 is rated for a maximum signal level of ±600 mV. A series resistor of 30 Ω reduces the output swing of the ADCLK925 below this value. The ADCLK925 output is AC coupled to the 50 Ω differential input of the ADF4106. The second output of the ADCLK925 is similarly terminated to provide the RFOUT signal.

PLL design and performance

ADIsimPLL™ software is used to design the loop filter of the PLL using the required low frequency values, namely 10 MHz REFIN and 100 MHz RFIN. The loop filter has a bandwidth of 818 Hz and a phase margin of 45°.

Figure 3 shows the ADIsimPLL simulated phase noise, showing that the ADF4106 PLL loop is locked at low frequencies and the incremental phase noise is very small.

The actual measured phase noise of the PLL system is shown in Figure 4.

The ADIsimPLL software used to generate loop filter components can also be used to simulate circuit performance. ADIsimPLL assumes that the REF IN and RF IN inputs provide sufficient signal slew rate and signal swing. ADIsimPLL allows the simulation of the reference source used by the ADF4106PLL, which for this setup is the R&S SMA100 signal generator.

When simulating the phase noise of a single-ended 10 MHz, 0 dBm reference input signal, measured values at offset values of 10 Hz and 1 MHz were used. An Agilent FSUP spectrum analyzer was used to measure the reference phase noise at these offset values.

In order to simulate VCO performance in ADIsimPLL, the ADCLK925 data sheet needs to be combined with the phase noise data of the CVSS-945 VCXO (Crystek Crystals, 12730 Commonwealth Drive, Fort Myers, Florida 33913), as shown in Table 1.

| phase noise offset |

ADCLK925 (dBc/Hz) | VCXO(dBc/Hz) | Total(dBc/Hz) |

| 10HZ | -140 | -86 | -86 |

| 1MHZ | -158 | -172 | -157 |

The phase noise value at 10 Hz offset in the ADCLK925 data sheet is −140 dBc, which has a negligible effect on the combined 1/f phase noise. The combined 1/f phase noise at 10 Hz offset is −86dBc/Hz. The combined phase noise at 1 MHz offset is −157 dBc/Hz.

In the data sheet, the ADCLK925 has a phase noise of –161 dBc/Hz at 1 MHz offset. This is measured differentially, so the measured noise floor in the data sheet needs to be adjusted by 3 dB when using the single-ended output. The phase noise of the VCXO is −172 dBc/Hz, and its contribution to the combined phase noise is almost negligible.

Comparison of measured results and simulation results

Table 2 shows the simulation results and measured results of phase noise and phase jitter. Phase noise is measured at offset values of 100 Hz, 2 kHz, and 100 kHz. Phase jitter is integrated from 100 Hz to 30 MHz. In this simulation, the ADIsimPLL program uses a point noise floor model for the reference source and VCO. As a result, the models in ADIsimPLL are very close to the 1/f noise and noise floor, but at intermediate offset values they can differ from the carrier by a few dB.

| parameter |

simulation | measured |

| PN Offset of 100Hz dBc/Hz |

-113dBc/Hz |

-114dBc/Hz |

| PN Offset of 2 kHz dBc/Hz |

-126dBc/Hz | -122dBc/Hz |

| PN Offset of 100 kHz dBc/Hz |

-156dBc/Hz | -156dBc/Hz |

| Phase Jitter(100Hz to 30MHz) | 208fs | 276fs |

Blockdiagram

All reference designs on this site are sourced from major semiconductor manufacturers or collected online for learning and research. The copyright belongs to the semiconductor manufacturer or the original author. If you believe that the reference design of this site infringes upon your relevant rights and interests, please send us a rights notice. As a neutral platform service provider, we will take measures to delete the relevant content in accordance with relevant laws after receiving the relevant notice from the rights holder. Please send relevant notifications to email: bbs_service@eeworld.com.cn.

It is your responsibility to test the circuit yourself and determine its suitability for you. EEWorld will not be liable for direct, indirect, special, incidental, consequential or punitive damages arising from any cause or anything connected to any reference design used.

Supported by EEWorld Datasheet