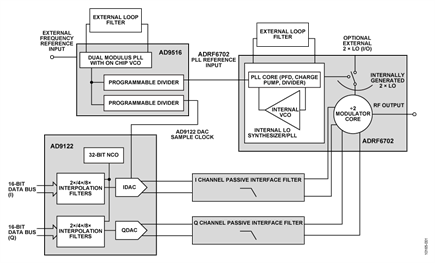

Combining the ADRF6702 IQ modulator and the AD9122 16-bit dual-channel 1.2 GSPS TxDAC meets the dynamic range requirements of modern high-level QAM or OFDM wireless transmitters (shown in Figure 1). The circuit's dynamic range is excellent enough to support both ZIF (zero IF/baseband) and CIF (composite IF up to 200 MHz to 300 MHz). The AD9122 has optional up to 8× interpolation and a 32-bit NCO for ultra-fine IF sensitivity.

The overall performance of a transmitter is closely related to the dynamic range of the components that directly make up the signal chain. In mixed-signal transmitters using DACs and IQ modulators, the noise floor and distortion characteristics of these components determine the overall dynamic range of the signal chain. However, the DAC's noise floor can also be exacerbated by sampling clock jitter, and IQ modulator performance depends on the noise and spurious characteristics of its local oscillator (LO). Therefore, using high-performance components for sampling clock and LO generation is the key to a high-performance transmitter.

Additionally, generating these signals as close as possible to the DAC and modulator on the PCB and using an external reference source can greatly simplify the design. Generating the clock and LO separately (the vast majority of LOs are multi-GHz signals) and at a distance from the DAC and IQ modulator requires very careful PCB layout. Even the slightest layout error can cause these critical signals to couple and degrade overall signal chain performance.

Signal chain performance also depends heavily on the DAC/IQ modulator interface filter. To optimize performance, it is recommended that this passive filter be designed after careful analysis of the required system specifications.

The ADRF6702 includes an onboard fractional PLL for LO generation so that only a low frequency reference (typically below 100 MHz) is needed to synthesize the IQ modulator LO. Using a PLL within the AD9516 clock generator allows one reference to generate both the DAC sampling clock and the PLL reference for the ADRF6702.

The circuit in Figure 1 was built using the AD9516-0, but other members of the AD9516 family may be used, depending on the desired internal VCO frequency.

ADRF6702 IQ modulator with internal LO synthesizer, synthesizer IQ modulator interface

The ADRF6702 IQ modulator is a unique device with several features. In addition to excellent dynamic range, it includes a fractional-N PLL that allows programming of discrete LO frequency steps below 25 kHz while still maintaining a small enough overall frequency multiplication to avoid phase noise from the reference to the synthesizer output. surge.

Another feature of the ADRF6702 is the divide-by-2 architecture of the IQ modulator. A conventional IQ modulator accepts an LO input frequency of 1x the desired LO. Internally, a distributed RC network generates the required in-phase and quadrature LO signals from a single LO frequency input. Because this is a passive RC network, the bandwidth to achieve quadrature modulation accuracy is limited. Also, for excellent quadrature accuracy, the external LQ should keep the spectrum pure. This traditional LO modulator architecture creates harmonics on the LO that may degrade the overall modulation accuracy. For this reason, when using a PLL synthesizer to generate the LO signal required by the IQ modulator, it is often necessary to configure a narrow transition band band-pass or low-pass filter at the LO input end of the IQ modulator.

In the ADRF6702's divide-by-2 LO architecture, a simple digital divider is used internally to produce near-perfect quadrature over a wide frequency band. The 2x LO is generated internally by the PLL synthesizer, so it does not need to be distributed around the PCB, and because the 2x LO architecture is only affected by the LO signal edges and not the frequency content, there is no need for any filters between the synthesizer and the IQ modulator LO. For details on the impact of LO harmonics on 1× IQ modulator and LO filter designs, see Circuit Note CN-0134 .

Signal sampling to RF, total background spurious

The baseband signal travels through several steps up to the RF transmit frequency. This signal starts in the discrete (sampling) domain and is synthesized by the DAC into the analog domain. This step causes the DAC to produce image and distortion products. As shown in Figure 2, an ideal DAC with no distortion would produce multiple images of the baseband signal, which must then be filtered before modulation. Most image energy can be suppressed using an interpolation filter such as the AD9122 series, but an analog interface filter is still required between the DAC and modulator. However, there is a trade-off between DAC interpolation and analog filter order. The higher the DAC interpolation rate, the lower the required analog filter order, and vice versa. As an example, Figure 3 shows the DAC output frequency waveform when using 4x interpolation.

Multiple RF spurious components coexist

This signal chain can significantly increase spurious content due to modulation products, distortion products, and integer multiples of the LO frequency. If we consider all the potential sources of spurs discussed, the spurious components include:

(j × LO_freq) + (k × DAC_sample_rate) +

(l × DAC_NCO_freq) + (m × DAC_input_IF)

where j, k, I and m are all integers between positive infinity and negative infinity.

DAC/Modulator Passive Interface Filters

The analog interface between the DAC and IQ modulator is key to reducing the overall spurious spectrum. The interface filter design between the DAC and IQ modulator must consider many aspects of performance.

DAC_MOD interface filter topology

Figure 5 shows a typical topology that produces the flattest Butterworth response of order 5 for 100 Ω differential input and output impedances. The actual response is shown in Figure 6. This filter uses 4.6 pF capacitors at the source impedance and load.

Capacitances of this order (<20 pF) represent filters with high cutoff frequencies. Parasitic capacitance can have a significant impact on frequency response when using these smaller capacitor values.

DAC and distortion related spurious components

Originally using a DAC interpolation filter can reduce the spurious components at the modulator input and therefore the spurious components at the RF output. However, significant spurious components may still be present. Figure 7 shows the RF output spectrum of the IQ modulator under the following conditions.

FLO = 1940 MHz

DAC input data rate = 300 MSPS

DAC interpolation = 4×

DAC frequency = 150 MHz

DAC input IF frequency = 8 MHz

Note that the strongest spurious component (excluding the 2098 MHz fundamental) is 2 times the 2400 MHz DAC clock component. This may be due to the fact that the common-mode and differential-mode components of the DAC output contain some of the spectrum from the DAC clock. Common-mode rejection at the IQ modulator input eliminates most of this signal, but it still contains a lot of energy. The next two highest spurs at 2062 MHz and 2242 MHz also appear to be related to DAC clock spurs. The spur at 2242 MHz can be easily expressed as 2 × (DAC clock – DAC fundamental frequency) = 2400 − 158. The spur at 2062 MHz is not as obvious, but is almost (3 × LO) − (3 × DAC clock) − 158 = 5820 − 3600 − 158. If the above analysis is correct and the common-mode component of the DAC clock can be suppressed at the IQ modulator input, then spurs should be significantly reduced.

As shown in Figure 8, applying a differential Butterworth filter can significantly reduce spurious levels. The strongest spurs are still at 2062 MHz, 2242 MHz, and the 2× DAC clock spur is at 2400 MHz. All three spurious components have been significantly reduced.

Changing the topology of the interface filter can often improve the common-mode rejection performance of the DAC/IQ modulator interface. In Figure 9, common-mode capacitors (9.0 pF) replace the input and output 4.7 pF capacitors from both sides of the filter input and from both sides of the filter output to ground. This does not change the overall differential filter mode response, but does affect the overall RF spurious content of this board. The above harmonics at 2062 MHz and 2242 MHz are reduced to a few dB, while the 2× DAC clock component is reduced by approximately 15dB, close to the noise floor.

The topologies and results shown here may vary depending on the layout, so designers are advised to experiment with filter layouts first, paying particular attention to mixing differential and common-mode capacitors to achieve the lowest overall spurious floor.

Synthesizer Path and PLL Phase Noise

As shown in Figure 1, this circuit uses an external reference to generate the AD9122 DAC sample clock and reference clock for the ADRF6702's PLL. The AD9516 is key to ensuring flexibility. The AD9516 has a built-in PLL and integrated VCO. It also contains several outputs that support differential LVPECL, LVDS, or single-ended CMOS programming, with independent divider settings for each output path. In this circuit, one of the output paths is used for the DAC clock, while the other output is used as the reference input of the ADRF6702 fractional-N PLL.

There are two benefits of using a fractional PLL in the ADRF6702. First, the fractional PLL allows ultra-fine tuning of the output LO. For example, when the input frequency is 38.4 MHz and the ADRF6702 programming MOD value is 1536, the LO can be programmed in 25 kHz increments. Second, the reference frequency does not have to be equal to the LO frequency/division ratio, and can be much higher, causing the division ratio to be reduced. Because the output phase noise is a function of the reference phase spur multiplied by the frequency division ratio, this means that the RF itself has low phase noise.

A key metric for a synthesizer system is the amount of phase noise added by the individual PLLs and dividers. Figure 10 shows the spectrum analyzer noise floor (green line), reference generator phase noise (red line), and output phase noise (yellow line) when the RF frequency is 1961 MHz and the LO is 1940 MHz. Using a PLL combination in the AD9516 and ADRF6702 does produce significantly higher near-carrier phase noise (offset carrier below 500 kHz), but does not significantly increase the broadband noise of the system. The loop filters of the VCOs in the AD9516 and ADRF6702 are both set to approximately 100 kHz bandwidth in the measurement circuit. Near-carrier phase noise can be reduced by reducing the bandwidth of these loop filters. Please review the system specifications carefully to determine the near-carrier phase noise that a given system can tolerate.

Blockdiagram

All reference designs on this site are sourced from major semiconductor manufacturers or collected online for learning and research. The copyright belongs to the semiconductor manufacturer or the original author. If you believe that the reference design of this site infringes upon your relevant rights and interests, please send us a rights notice. As a neutral platform service provider, we will take measures to delete the relevant content in accordance with relevant laws after receiving the relevant notice from the rights holder. Please send relevant notifications to email: bbs_service@eeworld.com.cn.

It is your responsibility to test the circuit yourself and determine its suitability for you. EEWorld will not be liable for direct, indirect, special, incidental, consequential or punitive damages arising from any cause or anything connected to any reference design used.

Supported by EEWorld Datasheet