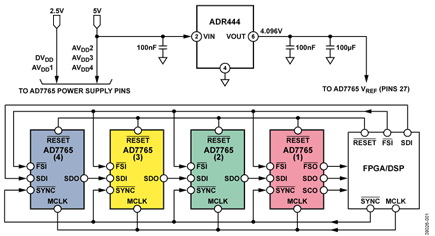

The circuit shown in Figure 1 provides a high dynamic range 4-channel simultaneous sampling system with high crosstalk isolation and flexible sampling rates, requires few external components, and can be easily connected to a DSP or FPGA. This circuit uses a daisy-chain configuration of four AD7765 Σ-Δ ADCs , so the number of connections to the digital host is minimized. The AD7765 fully integrates differential input/output amplifiers and reference buffers, significantly reducing the number of external components required.

Using the AD7765 configured for simultaneous sampling provides the following advantages:

Each AD7765 is clocked using a common sample clock (MCLK), synchronization signal ( SYNC ), and reset signal ( RESET ), as shown in Figure 1. The 4.096 V common reference voltage provided by the ADR444 (using the circuit shown in Figure 5) is applied to each AD7765 in a star single-point configuration (each ADC has a built-in reference voltage buffer).

A RESET pulse is applied to all devices at power-up (the minimum low time of the pulse is 1 × MCLK period). The rising edge of RESET (which takes the ADC out of reset) is applied to each AD7765 to synchronize with the falling edge of MCLK. A SYNC pulse (minimum low time 4 × MCLK periods) is then applied to all AD7765 devices, which gates the AD7765's digital filter (when it is logic low). On the first MCLK falling edge after SYNC returns to a logic high level, the AD7765's digital filter begins processing samples internally.

The SYNC function plays the following two roles:

Once all devices are synchronized, all ADCs can be configured. Daisy chain operation requires all ADCs to use the same decimation rate (controlled by pin 18) and power mode (controlled by writing to control register address 0x0001) settings to ensure synchronous data output from each device.

To write to all four devices in the daisy chain, a common FSI (frame synchronization input) signal is applied to all AD7765s. The write operation to the AD7765 consists of 32 bits (16 address bits, 16 register bits). FSI transfers data to the device in frames. When writing to all four devices, the SDI input of the daisy chain is loaded using a single data write instruction, that is, when FSI goes low, 32 bits of data are written to the SDI (serial data input) of the AD7765 (4).

The examples in this note operate in normal power mode with a decimation factor of 128 (maximum output data rate of 156 kSPS).

Reading data from the daisy chain

Only one FSO (Frame Sync Out) signal is applied to the digital host as an interrupt for reading data from the daisy chain ( FSO (1)). This signal is the frame signal for all four channels. The data format read back from the digital host (FPGA or DSP) is shown in Figure 3. The conversion data and status bits of AD7765 (1) are output first ( FSO (1) is active low during this period ), followed by the conversion data and status bits of AD7765 (2), (3), and (4). Note that FSO (1) is logic high when data results are output from the remaining converters in the daisy chain .

The next time FSO (1) transitions from logic high to logic low, it indicates that the next set of sample points for all four channels is available for readback. The digital host needs to start the readback on the falling edge of FSO (1) and read back 4 × 32 bits, or 128 bits, from the SDO (1) serial output. The data output on SDO (Serial Data Output) is synchronized with the SCO (Serial Clock Output).

performance

The AD7765 daisy chain circuit allows the user to simultaneously sample up to 4 channels at an output data rate of 156 kSPS. The output data rate can be changed by reducing the MCLK frequency or changing the decimation rate of the AD7765. After changing the decimation rate, it is recommended to resynchronize these ADCs. Figure 4 shows the output FFT of the AD7765 (3) operating at a maximum sampling rate of 156 kSPS and a MCLK frequency of 40 MHz. A −0.5 dBFS input signal is applied to the differential amplifier input of the AD7765 at a 1 kHz input frequency.

Figure 5 shows the output FFT of the AD7765 (3) operating at a sampling rate of 97.65 kSPS, a MCLK frequency of 25 MHz, and an input signal of 1 kHz (−0.5 dBFS). Table 1 lists the performance of the AD7765 in 40 MHz, 30 MHz, 25 MHz, 20 MHz, and normal power modes.

| MCLK(MHz) | 20MHz | 25MHz | 30 MHz | 40MHz | ||||

|

−3 dB PASS-BAND

ANALOG INPUT BW

|

31.25kHz | 39.0625kHz | 46.3875kHz | 62.5kHz | ||||

|

STAR POINT

CAPACITOR

|

10µF | 100µF | 10µF | 100µF |

10µF | 100µF |

10µF | 100µF |

| SNR(dBFS) | 106.16 | 107.40 | 106.29 | 106.83 | 106.27 | 106.96 | 105.53 | 106.45 |

| SINAD (dBFS) | 102.92 | 103.26 | 102.40 | 102.86 | 102.39 | 102.16 | 101.19 | 101.70 |

| THD (dB) | −105.74 | −105.41 | −104.75 | −105.13 | −104.73 | −103.97 | −103.26 | −103.55 |

The signal source is Audio Precision SYS2522 analog output, balanced GND, 7.699 V pp output, 40 Ω output impedance, high precision mode. The analog inputs are applied directly to the AD7765's integrated differential amplifier. The number of FFT sampling points is 131,072.

crosstalk

A major performance advantage of implementing multi-channel simultaneous sampling with discrete ADCs rather than integrated devices is high crosstalk isolation. Table 2 lists the crosstalk on adjacent channels of the AD7765 when a −0.5 dB, 1 kHz input signal is applied to the AD7765 (2).

| ADC Channel |

AD7765 (1) | AD7765 (2) | AD7765 (3) | AD7765 (4) |

| Crosstalk (dB) |

−125dB | N/A | −125dB | −130dB |

| Input Voltage |

Pins 1 and 3 Shorted to GND |

−0.5 dBFS 1 kHz input |

Pins 1 and 3 Shorted to GND |

Pins 1 and |

Reference voltage configuration

The ADR444 provides a 4.096 V reference voltage for each AD7765 device in this circuit. One of the advantages of the AD7765 is the on-chip integrated reference buffer, which isolates the user from the internal reference sampling circuitry. This means that when multiple devices share the same reference voltage, no external buffer is required. The star single-point configuration shown in Figure 6 allows the reference voltage to be applied to each ADC from a single point through parallel traces. This is a best practice to minimize potential interactions between ADCs. The reference voltage is tapped serially to each device from a common reference voltage trace. Additionally, an on-chip reference buffer isolates the internal dynamically switched capacitive load from the single point of the star.

Blockdiagram

All reference designs on this site are sourced from major semiconductor manufacturers or collected online for learning and research. The copyright belongs to the semiconductor manufacturer or the original author. If you believe that the reference design of this site infringes upon your relevant rights and interests, please send us a rights notice. As a neutral platform service provider, we will take measures to delete the relevant content in accordance with relevant laws after receiving the relevant notice from the rights holder. Please send relevant notifications to email: bbs_service@eeworld.com.cn.

It is your responsibility to test the circuit yourself and determine its suitability for you. EEWorld will not be liable for direct, indirect, special, incidental, consequential or punitive damages arising from any cause or anything connected to any reference design used.

Supported by EEWorld Datasheet