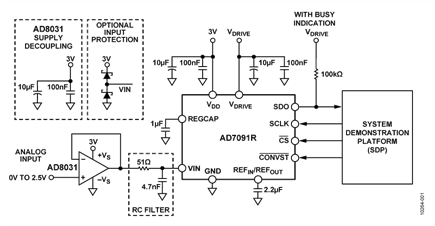

The circuit in Figure 1 is an ultra-low-power data acquisition system using the AD7091R 12-bit, 1 MSPS SAR ADC and AD8031 op amp driver. The total power consumption of the circuit is less than 5 mW and operates from a single 3 V power supply.

The low power consumption and small package size of the selected devices make this combination an industry-leading solution for portable battery-powered systems where power consumption, cost and size are critical.

When the VDD pin is 3 V, the AD7091R's supply current is only 350μA typical, which is significantly lower than any competing ADC product currently on the market. This means typical power consumption is about 1 mW.

The AD8031 requires only 800 μA of supply current and consumes a typical power consumption of 2.4 mW at a supply voltage of 3 V. The total system power consumption is less than 5 mW when sampling at 1 MSPS with a 10 kHz analog input signal.

For analog signals, most SAR ADCs require suitable input buffers for optimal performance. The buffer isolates the signal source from transients generated at the ADC input when the internal sample-and-hold switch switches from hold to sample. The buffer driving the ADC must recover from this transient and settle to the required accuracy within the ADC acquisition time. This is particularly important in applications where the signal source has high impedance and low distortion and high signal-to-noise ratio are critical. Therefore, choosing the appropriate buffer op amp becomes an extremely important part of the design.

The AD7091R is a 12-bit, fast, ultra-low power, single-supply ADC with an integrated 2.5 V internal reference. The device operates from 2.7V to 5.25V supplies. The AD7091R has a throughput rate of up to 1MSPS. When the input signal is 10kHz and the sampling rate is 1MSPS, the total power consumption of the device is approximately 2.3 mW.

In applications that do not require a 1MSPS sampling frequency, this number will drop because the power consumption of the AD7091R is proportional to the throughput rate, as shown in Table 1.

Power consumption can be further reduced by reducing the throughput rate of the converter. Table 1 shows the typical power consumption versus throughput rate of the AD7091R when the supply is 3 V and the device is operating in normal mode.

Table 1 shows the power consumption reduction that can be achieved by activating shutdown mode. When the AD7091R is operating at lower throughput rates, shutdown mode is extremely effective at significantly reducing power requirements.

The AD7091R is available in a small 3 mm × 2 mm, 10-lead LFCSP or 3 mm × 5 mm, 10-lead MSOP package. Both packages significantly save space compared to similar competing solutions.

The AD8031 is a low-power rail-to-rail input/output operational amplifier that is a very suitable driver amplifier for the AD7091R. The AD8031 operates from a 2.7V to 1 V supply and supports driving two ICs from a single supply rail. The AD8031 has an 80MHz bandwidth, a slew rate of 30V/μs, and a settling time of 125 ns to 0.1% accuracy.

When operating from a single supply, the AD8031 output can reach within 20mV of the negative supply rail. If linearity at 0V input is required, the AD8031 requires an additional negative supply (refer to Tutorial MT-035 ).

Figure 1 shows a simplified circuit diagram. Use 100 nF and 10μF ceramic capacitors to achieve good ground decoupling of the IC power pins. Place these capacitors as close as possible to the power pins of both ICs.

Remember, the analog input signal to this ADC cannot exceed the supply rail by more than 300 mV. If the signal exceeds this level, the internal ESD protection diodes become forward biased and begin conducting current into the substrate. The maximum conduction current of the diode is 10 mA, and irrecoverable device damage will not be caused below this current. Protection can be achieved by connecting a pair of Schottky diodes between VIN and the power rail of the AD7091R, as described in tutorial MT-036.

The AD7091R integrates an internal 2.5 V reference. Good decoupling of the REF IN /REF OUT pins achieves the specified performance. The typical value of the REFIN/REFOUT capacitor is 2.2μF. Note that the internal reference voltage can be externally loaded.

If an external reference voltage is used, the voltage range must be 2.7V to VDD and the REFIN/REFOUT pin must be connected. The typical value of the regulator bypass (REGCAP) decoupling capacitor is 1µF.

The voltage applied to the V DRIVE input controls the logic-level voltage of the serial interface. Connect this pin to the supply voltage of the logic family, which is connected to the AD7091R digital output. V DRIVE can be set to a value in the range 1.8 V to VDD. A typical value for the VDRIVE decoupling capacitor is 100nF in parallel with 10µF.

If the busy indicator function is required, a 100kΩ pull-up resistor can be connected between the V DRIVE and SDO pins.

The AD8031 used to buffer the analog input of the AD7091R is configured as a unity gain buffer. Connect a single-pole RC filter after the op amp's output stage to reduce out-of-band noise. The cutoff frequency of the RC filter is set to 660kHz. However, this parameter may vary depending on the system throughput rate requirements. For systems where the AD7091R is not operating at the maximum throughput rate, the filter cutoff frequency can be reduced. Depending on the input amplitude and offset of the analog signal, the AD8031 op amp can be configured to provide gain, attenuation, and level translation to match the input signal swing of the ADC analog input range.

| model |

IDD |

I DRIVE |

I AMP (µA) |

Total current (µA) |

Total power consumption (mW) |

| turn off |

550nA |

36nA |

766 |

767 |

2.3 |

| Static (power on, input grounded, no clock) |

21 µA |

81nA |

766 |

787 |

2.4 |

| Operation (power on, 10 kHz input, 1 MSPS sampling) |

368 µA |

406 µA |

766 |

1540 |

4.6 |

| Operation (power on, input ground, 1 MSPS sampling) |

344 µA |

35 µA |

766 |

1145 |

3.4 |

| Operation (power on, input ground, 1 kSPS sampling) |

57.8 µA |

18.9 µA |

766 |

843 |

2.5 |

Note that when sampling, the conversion start pulse width = 20 ns, V DD =V DRIVE = 3 V.

Figures 2 and 3 show the integral nonlinearity (INL) and differential nonlinearity (DNL) curves of the circuit. Note that INL and DNL are less than ±1 LSB.

Figure 4 shows the FFT data calculated for 8192 samples; the sampling rate is 1MSPS and the analog input frequency is 10 kHz. SNR is 70.44 dBFS.

The circuit must be built on a multilayer printed circuit board (PCB) with a large area ground plane. For optimal performance, proper layout, grounding, and decoupling techniques must be used (refer to Tutorial MT-031 , Tutorial MT-101 , and the CN-0247 Design Support Package demonstrating AD7091R evaluation board layout).

Depending on the specific requirements of the application and sensor, the device values around the AD7091R and AD8031 can be changed. For example, the buffer can be configured to provide gain and offset, and the cutoff frequency of the RC filter can vary depending on the sampling frequency and input frequency.

For a complete documentation package, including schematics, board layout, and bill of materials (BOM), please refer to http://www.analog.com/CN0247-DesignSupport

Blockdiagram

All reference designs on this site are sourced from major semiconductor manufacturers or collected online for learning and research. The copyright belongs to the semiconductor manufacturer or the original author. If you believe that the reference design of this site infringes upon your relevant rights and interests, please send us a rights notice. As a neutral platform service provider, we will take measures to delete the relevant content in accordance with relevant laws after receiving the relevant notice from the rights holder. Please send relevant notifications to email: bbs_service@eeworld.com.cn.

It is your responsibility to test the circuit yourself and determine its suitability for you. EEWorld will not be liable for direct, indirect, special, incidental, consequential or punitive damages arising from any cause or anything connected to any reference design used.

Supported by EEWorld Datasheet