This circuit provides a simple and flexible interface between the AD9122 dual-channel high-speed TxDAC digital-to-analog converter and the wideband I/Q modulator ADL5375-05. Since the DAC output has the same 0.5 V bias level as the ADL5375-05I /Q modulator input, there is no need to use any active or passive level translation circuitry. This DC-coupled interface helps the DAC compensate for the local oscillator (LO) leakage of the I/Q modulator.

The AD9122 DAC's 1.2 GSPS sampling rate and the wide bandwidth of the ADL5375-05 modulator I/Q inputs ensure that both zero-IF (ZIF) and complex-IF (CIF) architectures are supported. In addition to filtering out the Nyquist image, the baseband filter provides excellent rejection of differential-mode and common-mode DAC spurs.

The circuit and evaluation board shown in Figures 1 and 2 use the AD9122 TxDAC and the ADL5375-05 wideband transmit modulator. The signal bias and adjustment in this interface circuit are controlled by 4 ground-based resistors (RBIP, RBIN, RBQP, RBQN) and 2 parallel resistors (RSLI, RSLQ).

The DAC's full-scale output current (I FS ) is programmable from 10 mA to 30 mA, with a nominal default value of 20 mA. In this configuration, the DAC output swings from 0 mA to 20 mA across four ground-referenced 50 Ω resistors (R B =RBIP = RBIN = RBQP = RBQN), resulting in a 500 mV DC bias. levels, and a 2 V pp differential full-scale voltage swing (no load) on each output pair. This 2 V pp voltage swing can be adjusted with the parallel resistor R L (R L = RSLI = RSLQ) without affecting the 500 mV bias level. Therefore, the differential peak-to-peak swing of the I/Q modulator input is given by:

Note that the relatively high differential input impedance of the ADL5375 (typically greater than 60 kΩ) can be ignored when calculating this signal level. Figure 3 shows the peak-to-peak voltage swing versus R L using a 50 Ω bias setting resistor .

The dynamic range and gain of the ADL5375-05 and AD9122 are well matched. Therefore, no active gain is required between devices. The I/Q modulator drive level can be fine-tuned as needed by adjusting the value of RL , as described above. For most applications, a RL value of 100 Ω is recommended, which results in a full-scale signal level of 1 V pp (DAC output at 0 dBFS).

Baseband filtering

A filter must be inserted between the AD9122 and the ADL5375 to eliminate Nyquist images, spurs, and broadband noise from the DAC. This filter should be placed between the DC bias setting resistor and the AC limiting resistor so that the DC bias setting resistor (RB in Figure 4) and the signal conditioning resistor (RL in Figure 4 ) can be easily Set the source and load resistances of the filter design.

Figure 4 shows a third-order Bessel low-pass filter with a −3 dB bandwidth of 10 MHz. The input and output impedances of this filter are matched, making filter design easy and achieving better passband flatness, enabling wide bandwidth filter designs. In this example, the parallel resistor selected is 100 Ω, resulting in an ac swing of 1 V pp differential. The frequency response curve of this filter is shown in Figure 5.

Filtering for complex intermediate frequency (CIF) applications

Figure 6 shows the frequency response of the ADL5375 baseband I and Q inputs. The device has a wide and flat frequency response (−3 dB point of 750 MHz), making it ideal for complex intermediate frequency (CIF) applications where the DAC output signal has been digitally upconverted. In complex IF applications, a low-pass Nyquist filter is still required, primarily because it maintains the DC offset level from the DAC output to the modulator input.

It is recommended to use the filter topology shown in Figure 7, which is a fifth-order Butterworth filter with a corner frequency of 300 MHz. A purely differential filter rejects differential-mode images, spurs, and noise from the DAC. Using two capacitors with a common connection to ground (C2 and C4 in Figure 7) to shunt a portion of the common-mode current to ground can achieve better common-mode rejection of high-frequency signals than a purely differential filter.

The simulated and measured responses of this filter are shown in Figure 8 and Figure 9 respectively. Measured flatness is ±0.6 dB from DC to 250 MHz and ±0.4 dB from 125 MHz to 250 MHz, obtained with the AD9122 anti-sinc function enabled. With this configuration, the common-mode rejection performance of the 2 × F DAC common-mode spurs versus common-mode frequency is shown in Figure 10 , both with and without the IF filter shown in Figure 7 .

Calculate the output power of AD9122 and ADL5375

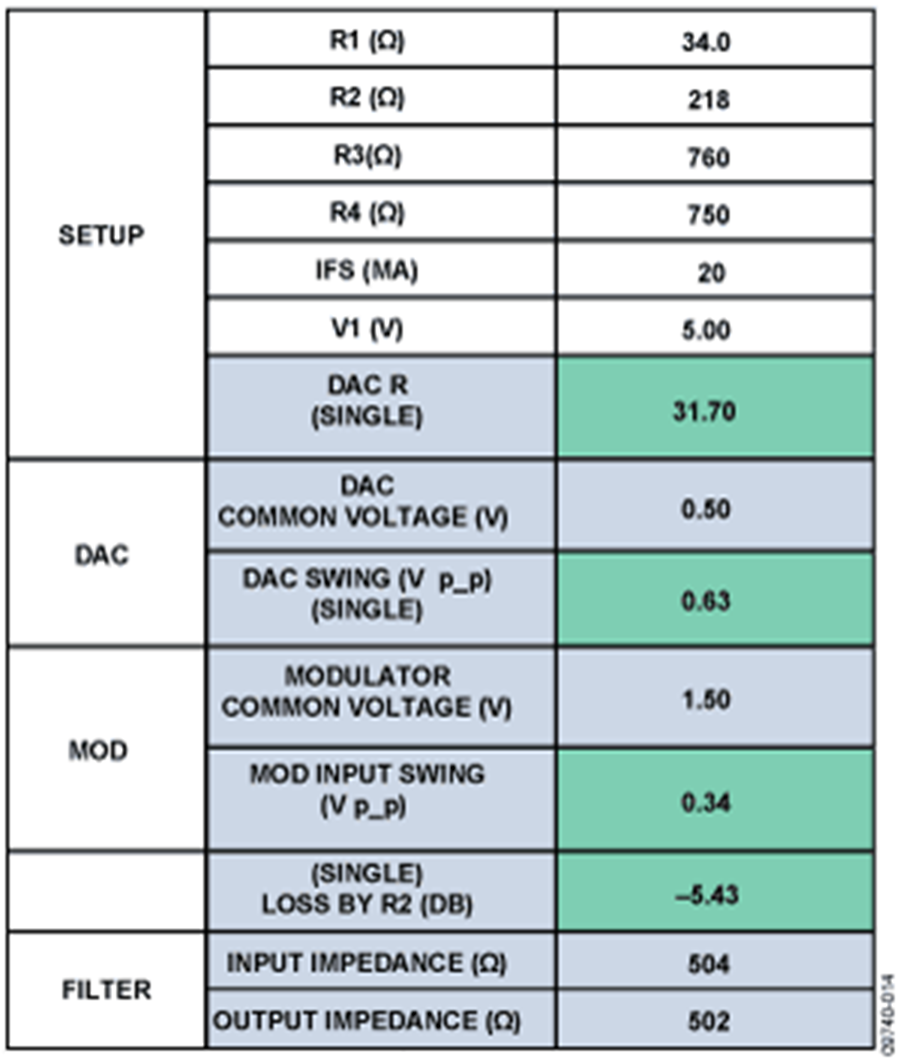

In addition to the bias setting and signal adjustment resistors, the ADL5375's output power level is also related to the digital setback level (dBFS) of the DAC, the peak-to-average ratio of the signal, the full-scale current of the DAC, the insertion loss of the Nyquist filter, and the I/ Related to the voltage gain of the Q modulator. The spreadsheet shown in Figure 11 can be used to calculate the output power.

The spreadsheet can be downloaded from the following URL: www.analog.com/CN0205-PowerCalculator

Converting levels to drive the ADL5375-15

The ADL5375-15 requires a DC bias level of 1500 mV. The ADL5375-05 is identical to the ADL5375-15 except for the bias levels. To drive the ADL5375-15 from the AD9122, a passive or active level translation network must be used. The passive level translation network shown in Figure 12 uses four series resistors and four pull-up resistors to achieve a bias level of 1500 mV at the ADL5375-15 input. This passive level translation network results in a loss of approximately 2 dB in signal level.

The active level conversion circuit uses a dual-channel differential amplifier, such as the ADA4938-2 , and the output DC bias level can be set by connecting the 1500 mV voltage to the VOCM pin. However, with this approach, the interface bandwidth is limited by the op amp.

As mentioned above, a filter needs to be placed between the AD9122 and the ADL5375-15. This LC filter can be located anywhere between the DAC termination resistor (R1 in Figure 13) and the AC limiting resistor (R4 in Figure 13). However, the circuit shown in Figure 13 allows flexibility in designing the level-shifting circuit, with lower R2 losses and higher drive levels for the modulator. It also allows the filter's source impedance to match the load impedance. It is recommended to use a passive level translation network with filters as shown in Figure 13.

The differential source impedance and load impedance of the filter are:

2 × (R1 + R2) and

2 × {R3||(R4/2)}

The single-ended impedance obtained by the DAC is:

R1||{R2+R3||(R4/2)}

R4 acts as the AC load for the DAC. The differential AC swing at the DAC output is:

2 × IFS × R1||{R2+R3||(R4/2)}

The differential AC swing at the modulator input is:

2 × {R3||(R4/2)}÷{R2+(R3||(R4/2)}

Multiply by the differential AC swing at the DAC output.

The LC filter should be placed close to the DAC to keep the loop current path short. The 5 V bias supply (V1) should be located close to the modulator because it is also used by the modulator. When R1, R2, R3, and R4 are 34 Ω, 218 Ω, 760 Ω, and 750 Ω respectively, the 500 mV DC bias voltage at the AD9122 DAC output matches the 1500 mV DC bias voltage of the ADL5375-15. In reality, the voltage at point A in Figure 13 does not have to be 500 mV, but it would allow some flexibility in the AC swing without exceeding the compliance voltage of the DAC output. The DAC load is 31.7 Ω. The input and output impedances of the filter are 504 Ω and 502 Ω respectively. The attenuation caused by R2, the voltage drop caused by R2 between the DAC output and the modulator input, is set by R2 and R3||(R4/2) and is approximately 5.4 dB.

To calculate the DC bias level and AC swing at points A and B (Figure 13), the attenuation due to R2, and the source/load impedance of the filter, use the spreadsheet below. The spreadsheet can be downloaded from the following URL: www.analog.com/CN0205-LevelShifter

The DAC and modulator power levels can also be calculated using the ADIsimRF tool, which can be downloaded from www.analog.com/ADIsimRF .

Layout and routing recommendations

Special attention should be paid to the layout of the DAC/modulator interface. Here are some suggestions. Figure 15 shows a top-level layout diagram that follows these recommendations.

For further information on proper layout and routing, review the AD9122-M5375-EBZ layout file in the design support package www.analog.com/CN0205-DesignSupport .

Blockdiagram

All reference designs on this site are sourced from major semiconductor manufacturers or collected online for learning and research. The copyright belongs to the semiconductor manufacturer or the original author. If you believe that the reference design of this site infringes upon your relevant rights and interests, please send us a rights notice. As a neutral platform service provider, we will take measures to delete the relevant content in accordance with relevant laws after receiving the relevant notice from the rights holder. Please send relevant notifications to email: bbs_service@eeworld.com.cn.

It is your responsibility to test the circuit yourself and determine its suitability for you. EEWorld will not be liable for direct, indirect, special, incidental, consequential or punitive damages arising from any cause or anything connected to any reference design used.

Supported by EEWorld Datasheet